#### **Features**

- ♦ Four channel full-duplex transceiver modules

- ♦ Hot pluggable QSFP+ form factor

- ♦ Four channel 850nm VCSEL Array

- ♦ Four channel PIN detector Array

- ♦ Data rate up to 10.5Gbps per channel

- → Maximum link length of 100m on OM3 MMF and 150m on OM4 MMF

- ♦ Maximum Power dissipation:<1W

- ♦ Single 1x12 MPO receptacle

- ♦ Single +3.3V power supply operating

- ♦ Built-in digital diagnostic functions

- ♦ Operating Case Temperature: 0°C~+85°C

- ♦ RoHS-6 compliant (lead-free)

# **Applications**

- ♦ 40G BASE-SR4/40G Ethernet

- ♦ Datacom switch and router connections

- ♦ Data centers and Metro networks

- ♦ Other Optical Links

### Standard

- ♦ Compliant with 40G Ethernet IEEE802.3ba

- ♦ Compliant with 40GBASE-SR4 Standard

- ♦ Compliant with SFF-8436 QSFP+ MSA

# **Description**

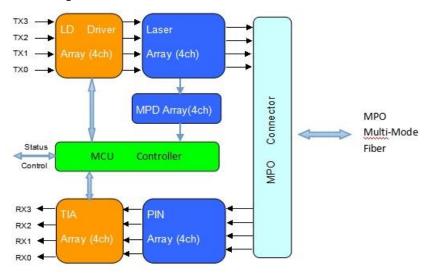

The QSFP+SR4 module is a 40Gb/s optical transceiver module for serial optical communication applications, The design is compliant to 40GBASE-SR4 of the IEEE P802.3ba standard, and transmission distance up to 100m on OM3 MMF and 150m on OM4 MMF. Digital diagnostics functions are available via an I2C interface as specified by the SFF-8436 QSFP+ MSA.

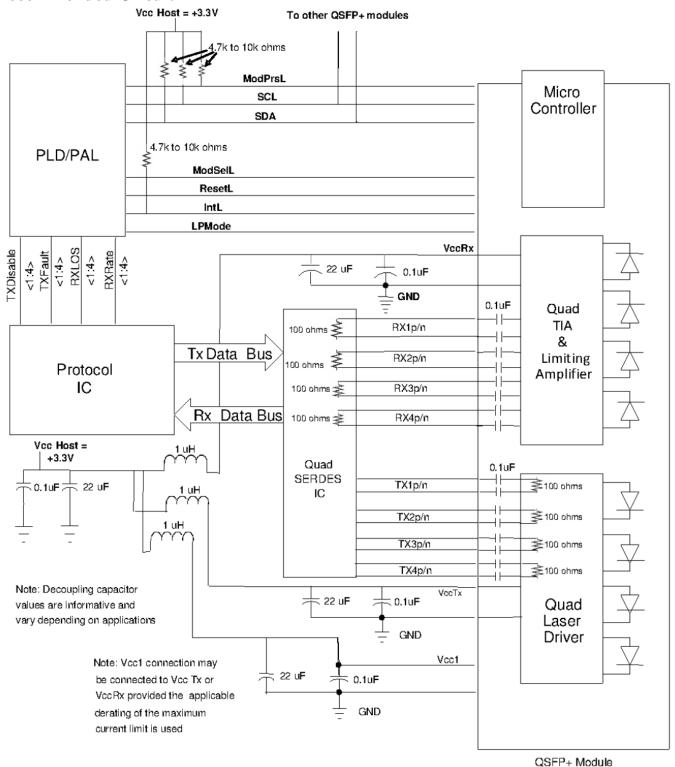

The module is hot pluggable into the 38-pin connector. The high-speed electrical interface is based on low voltage logic, with nominal 100 Ohms differential impedance and AC coupled in the module. The module have 5 low speed pins for control and status. Modseil is module select, Resetl is module reset, LPMode is Low Power Mode, Modprsl is module present, Intl is Interrupt.

om <u>Http://www.hioptel.com</u> Issued Date: 2019-04-30

Page 1 of 10 Rev2.3

## A block diagram of QSFP+SR4 optical transceiver is shown below

# **Specification**

**Absolute Maximum Ratings**

| Parameter                  | Symbol | Min | Max  | Unit          |

|----------------------------|--------|-----|------|---------------|

| Storage Temperature        | TST    | -20 | +85  | ${\mathbb C}$ |

| Operating Case Temperature | Тор    | 0   | +85  | $^{\circ}$    |

| Supply Voltage             | VCC3   | 0.0 | +3.6 | V             |

| Relative Humidity          | RH     | 5   | 95   | %             |

**Recommend Operation Environment**

| Secomment operation Environment |        |      |         |      |                                                                                    |

|---------------------------------|--------|------|---------|------|------------------------------------------------------------------------------------|

| Parameter                       | Symbol | Min  | Тур     | Max  | Unit                                                                               |

| Date Rate(per channel)          |        |      | 10.3125 |      | Gb/s                                                                               |

| Supply Voltage                  | VCC    | 3.13 | 3.3     | 3.47 | V                                                                                  |

| Supply Current                  | ICC    |      |         | 300  | mA                                                                                 |

| Power Dissipation               | PD     |      |         | 1.0  | W                                                                                  |

| Operating Case Temperature      | TOP    | 0    |         | +85  | $^{\circ}\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!$ |

Issued Date: 2019-04-30

Page 2 of 10

Rev2.3

Page 3 of 10

Rev2.3

**Optical Characteristics (Condition: Ta=TOP)**

| Parameter                                              | Symbol | Min                                  | Type    | Max  | Unit  | Note |

|--------------------------------------------------------|--------|--------------------------------------|---------|------|-------|------|

| Transmitter                                            |        |                                      |         |      |       |      |

| Date Rate(per channel)                                 |        |                                      | 10.3125 |      | Gb/s  |      |

| Optical Wavelength                                     | λ0     | 840                                  | 850     | 860  | nm    |      |

| RMS Spectrum Width                                     | Δλ     | -                                    | -       | 0.65 | nm    |      |

| Average output power, each lane                        | Po     | -7.5                                 | -       | 2.5  | dBm   | 1    |

| Optical Modulation Amplitude, each Lane                | OMA    | -5.6                                 | -       | 3.0  | dBm   |      |

| Difference in Launch Power between any two Lanes (OMA) |        | -                                    | -       | 4    | dB    |      |

| Optical Extinction Ratio                               | ER     | 3                                    |         |      | dB    | 1    |

| Dispersion penalty, each lane                          |        |                                      |         | 3.5  | dB    |      |

| Optical Return Loss Tolerance                          |        | -                                    | -       | 12   | dB    |      |

| Average Launch Power OFF Transmitter, each Lane        | Poff   |                                      |         | -30  | dBm   |      |

| Relative Intensity Noise                               | Rin    |                                      |         | -128 | dB/HZ |      |

| Eye Mask definition(X1,X2,X3,Y1,Y2,Y3)                 |        | 0.23, 0.34, 0.43,<br>0.27, 0.35, 0.4 |         |      |       |      |

| Receiver                                               |        |                                      |         |      |       |      |

| Date Rate(per channel)                                 |        |                                      | 10.3125 |      | Gb/s  |      |

| Receiver Sensitivity, each Lane                        |        | -                                    | -       | -9.5 | dBm   | 2    |

| Maximum Receiver Power, each lane                      |        | 2.4                                  | -       | -    | dBm   | 2    |

| Receiver Power (OMA), each Lane                        |        |                                      |         | 3.0  | dB    |      |

| Stressed Receiver Sensitivity in OMA each Lane         |        |                                      |         | -5.4 | dBm   |      |

| LOS De-Assert                                          | LOSD   |                                      |         | -12  | dBm   |      |

| LOS Assert                                             | LOSA   | -30                                  |         |      | dBm   |      |

| LOS Hysteresis                                         |        | 0.5                                  |         |      | dB    |      |

| Receiver Reflectance                                   |        |                                      |         | -12  | dB    |      |

#### **Notes:**

Note 1) Measured at 10.3125Gb/s with PRBS  $2^{31} - 1$  NRZ test pattern. Note 2) Measured at 10.3125Gb/s with PRBS  $2^{31} - 1$  NRZ test pattern for BER  $< 1 \times 10^{-12}$

Shenzhen Hi-Optel Technology Co., Ltd.

Hi-Optel Building,BLOG2,Gaofa Technology Park,Longjing,Nanshan Shenzhen,China. 518055 Tel: +86 755 2675 3088 Fax: +86 755 2675309

E-mail: info@hioptel.com Http://www.hioptel.com Issued Date: 2019-04-30

## **Electrical Characteristics (Condition: Ta=TOP)**

| Parameter                                | Symbol | Min | Тур | Max  | Unit | Note |

|------------------------------------------|--------|-----|-----|------|------|------|

| Supply Current                           | Icc    |     |     | 300  | mA   |      |

| Control I/O Voltage-High                 | VIH    | 2.0 |     | Vcc  | V    |      |

| Control I/O Voltage-Low                  | VIL    | 0   |     | 0.8  | V    |      |

| RESETL Duration                          |        |     | 10  |      | Us   |      |

| RESETL De-assert time                    |        |     |     | 100  | ms   |      |

| Power On Time                            |        |     |     | 100  | ms   |      |

| Transmitter                              |        |     |     |      |      |      |

| Differential input voltage swing         | VI     | 150 |     | 1200 | mVpp | 1    |

| Common mode voltage tolerance            |        | 15  |     |      | mV   |      |

| Input Differential Impedance             | Zin    | 80  | 100 | 120  | Ω    |      |

| Receiver                                 |        |     | •   |      |      |      |

| Differential output voltage swing        |        | 370 |     | 900  | mVpp | 2    |

| Rx Output Rise and Fall Time(20% to 80%) | Tr/Tf  | 28  |     |      | ps   |      |

| Output Differential Impedance            | Zon    | 80  | 100 | 120  | Ω    |      |

#### **Notes:**

- 1) TD+/- are internally AC coupled with  $100\Omega$  differential termination inside the module.

- 2) RD+/- outputs are internally AC coupled, and should be terminated with  $100\Omega$  (differential) at the user SERDES.

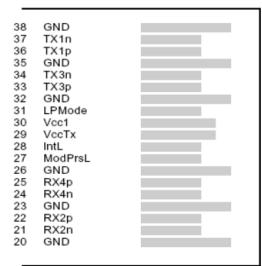

# **Pin Assignment**

Diagram of Host Board Connector Block Pin Numbers and Name

Shenzhen Hi-Optel Technology Co., Ltd.

Hi-Optel Building,BLOG2,Gaofa Technology Park,Longjing,Nanshan Shenzhen,China. 518055 Tel: +86 755 2675 3088 Fax: +86 755 2675309 E-mail: info@hioptel.com Http://www.hioptel.com Page 4 of 10 Rev2.3 Issued Date: 2019-04-30

# **Pin Description**

| Pin | Logic      | Symbol  | Name/Description                     | Ref. |

|-----|------------|---------|--------------------------------------|------|

| 1   |            | GND     | Ground                               | 1    |

| 2   | CML-I      | Tx2n    | Transmitter Inverted Data Input      |      |

| 3   | CML-I      | Tx2p    | Transmitter Non-Inverted Data output |      |

| 4   |            | GND     | Ground                               | 1    |

| 5   | CML-I      | Tx4n    | Transmitter Inverted Data Output     |      |

| 6   | CML-I      | Tx4p    | Transmitter Non-Inverted Data Output |      |

| 7   |            | GND     | Ground                               | 1    |

| 8   | LVTTL-I    | ModSelL | Module Select                        |      |

| 9   | LVTTL-I    | ResetL  | Module Reset                         |      |

| 10  |            | VccRx   | +3.3V Power Supply Receiver          | 2    |

| 11  | LVCMOS-I/O | SCL     | 2-Wire Serial Interface Clock        |      |

| 12  | LVCMOS-I/O | SDA     | 2-Wire Serial Interface Data         |      |

| 13  |            | GND     | Ground                               | 1    |

| 14  | CML-O      | Rx3p    | Receiver Inverted Data Output        |      |

| 15  | CML-O      | Rx3n    | Receiver Non-Inverted Data Output    |      |

| 16  |            | GND     | Ground                               | 1    |

| 17  | CML-O      | Rx1p    | Receiver Inverted Data Output        |      |

| 18  | CML-O      | Rx1n    | Receiver Non-Inverted Data Output    |      |

| 19  |            | GND     | Ground                               | 1    |

| 20  |            | GND     | Ground                               | 1    |

| 21  | CML-O      | Rx2n    | Receiver Inverted Data Output        |      |

| 22  | CML-O      | Rx2p    | Receiver Non-Inverted Data Output    |      |

| 23  |            | GND     | Ground                               | 1    |

| 24  | CML-O      | Rx4n    | Receiver Inverted Data Output        |      |

| 25  | CML-O      | Rx4p    | Receiver Non-Inverted Data Output    |      |

| 26  |            | GND     | Ground                               | 1    |

| 27  | LVTTL-O    | ModPrsL | Module Present                       |      |

| 28  | LVTTL-O    | IntL    | Interrupt                            |      |

| 29  |            | VccTx   | +3.3V Power Supply Transmitter       | 2    |

| 30  |            | Vcc1    | +3.3V Power Supply                   | 2    |

| 31  | LVTTL-I    | LPMode  | Low Power Mode                       |      |

| 32  |            | GND     | Ground                               | 1    |

| 33  | CML-I      | Tx3p    | Transmitter Inverted Data Output     |      |

| 34  | CML-I      | Tx3n    | Transmitter Non-Inverted Data Output |      |

| 35  |            | GND     | Ground                               | 1    |

| 36  | CML-I      | Tx1p    | Transmitter Inverted Data Output     |      |

| 37  | CML-I      | Tx1n    | Transmitter Non-Inverted Data Output |      |

| 38  |            | GND     | Ground                               | 1    |

**Shenzhen Hi-Optel Technology Co., Ltd.**Hi-Optel Building,BLOG2,Gaofa Technology Park,Longjing,Nanshan Shenzhen,China. 518055 Tel: +86 755 2675 3088 Fax: +86 755 2675309 E-mail: info@hioptel.com Http://www.hioptel.com

Page 5 of 10 Rev2.3 Issued Date: 2019-04-30

## 40G QSFP+ Transceiver HQSFP10-381 850nm VCSEL, MPO Connector, 0~85°C, 100m

#### **Notes:**

1)GND is the symbol for single and supply(power) commom for QSFP modules, All are common within the QSFP module and all module voltages are referenced to this potential otherwise noted. Connect these directly to the host board signal common ground plane.

2)VccRx, Vcc1 and VccTx are the receiver and transmitter power suppliers and shall be applied concurrently. Recommended host board power supply filtering is shown below. VccRX, Vcc1 and VccTx may be internally connected within the QSFP transceiver module in any combination. The connector pins are each rated for maximum current of 500mA

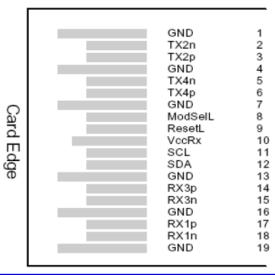

## **Digital Diagnostic Monitoring Interface**

Digital diagnostics monitoring function is available on QSFP+ SR4. Real time monitoring include Module temperature, Module supply voltage, and monitoring for each transmit and receive channel. the Memory Map for QSFP+ Module used for serial ID, digital monitoring and certain control functions. The interface is mandatory for all QSFP+ devices. The interface has been designed largely after the XFP MSA as defined in INF-8077i Rev.4.0. The memory map has been changed in order to accommodate 4 optical channels and limit the required memory space. The single address approach is used as found in XFP. Paging is used in order to enable time critical interactions between host and Module.

The structure of the memory is shown in Figure 30. The memory space is arranged into a lower, single page, address space of 128 bytes and multiple upper address space pages. This structure permits timely access to addresses in the lower page, e.g. Interrupt Flags and Monitors. Less time critical entries, e.g. serial ID information and threshold settings, are available with the Page Select function. The structure also provides address expansion by adding additional upper pages as needed. For example, in table1 upper pages 01 and 02 are optional. Upper page 01 allows implementation of Application Select Table, and upper page 02 provides user read/write space. The lower page and upper page 00 are always implemented. Page 03 is required if byte 2, bit 2 in the lower page is low. See Table 39 for details regarding declaration of optional upper pages 01 and 02. The interface address used is A0xh and is mainly used for time critical data like interrupt handling in order to enable a "one-time-read" for all data related to an interrupt situation. After an Interrupt, IntL, has been asserted, the host can read out the flag field to determine the effected channel and type of flag.

Issued Date: 2019-04-30

Page 6 of 10

Rev2.3

**Table 1.** Digital Diagnostic Memory Map (Specific Data Field Descriptions)

Hi-Optel Building,BLOG2,Gaofa Technology Park,Longjing,Nanshan Shenzhen,China. 518055 Tel: +86 755 2675 3088 Fax: +86 755 2675309 E-mail: info@hioptel.com Http://www.hioptel.com Page 7 of 10 Rev2.3 Issued Date: 2019-04-30

### **Table 2** - EEPROM Serial ID Memory Contents (**A0h**)

| Address | Description                                              | Type       | Passive Copper,  | Optical |  |

|---------|----------------------------------------------------------|------------|------------------|---------|--|

|         |                                                          |            | Active Copper,   | Module  |  |

|         |                                                          |            | Active Optical   |         |  |

| 0       | Identifier (1                                            | Read-Only  | R                | R       |  |

|         | Byte)                                                    |            |                  |         |  |

| 1-2     | Status (2 Bytes)                                         | Read-Only  | See Table 18     |         |  |

| 3-21    | Interrupt Flags<br>(19 Bytes)                            | Read-Only  | See Tables 19-21 |         |  |

| 22-33   | Module Monitors<br>(12 Bytes)                            | Read-Only  | See Table 22     |         |  |

| 34-81   | Channel Monitors<br>(48 Bytes)                           | Read-Only  | See Table 23     |         |  |

| 82-85   | Reserved (4 Bytes)                                       | Read-Only  | Reserved         |         |  |

| 86-97   | Control (12 Bytes)                                       | Read/Write | See Table 24     |         |  |

| 98-99   | Reserved (2 Bytes)                                       | Read/Write | Reserved         |         |  |

| 100-106 | Module and Channel<br>Masks (7 Bytes)                    | Read/Write | See Table 25     |         |  |

| 107-118 | Reserved (12<br>Bytes)                                   | Read/Write | Reserved         |         |  |

| 119-122 | Password Change<br>Entry Area<br>(optional) (4<br>Bytes) | Read/Write | 0 0              |         |  |

| 123-126 | Password Entry<br>Area (optional) 4<br>Bytes             | Read/Write | 0 0              |         |  |

| 127     | Page Select Byte                                         | Read/Write | R                | R       |  |

**Shenzhen Hi-Optel Technology Co., Ltd.**Hi-Optel Building,BLOG2,Gaofa Technology Park,Longjing,Nanshan Shenzhen,China. 518055 Tel: +86 755 2675 3088 Fax: +86 755 2675309 E-mail: info@hioptel.com Http://www.hioptel.com

Page 8 of 10 Rev2.3 Issued Date: 2019-04-30

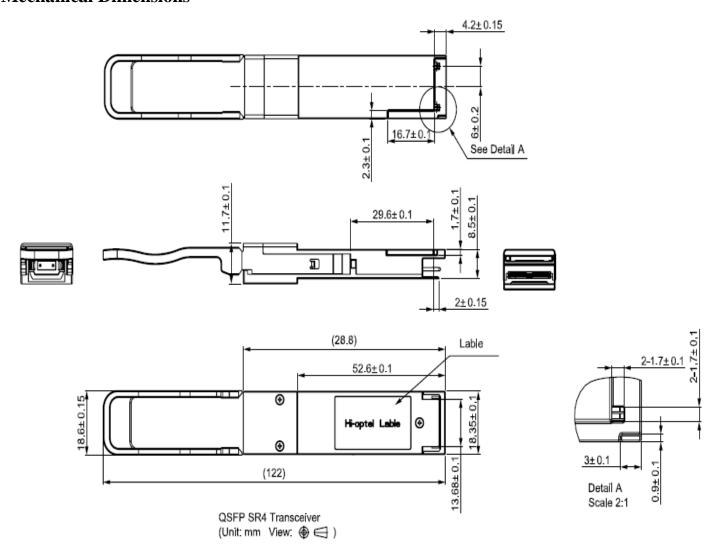

## **Mechanical Dimensions**

### **Recommended Circuit**

**Recommended High-speed Interface Circuit**

E-mail: info@hioptel.com Http://www.hioptel.com Issued Date: 2019-04-30